JAJU446A December 2017 – January 2022

- 概要

- Resources

- 特長

- アプリケーション

- 5

- 1 System Description

- 2 System Overview

- 3 Circuit Design

- 4 Host Interface

- 5 Hardware Functional Block

- 6 Getting Started Application GUI

- 7 Testing and Results

- 8 Design Files

- 9 Software Files

- 10Related Documentation

- 11About the Authors

- 12Revision History

7.4 Performance Test Result

Figure 7-4, Figure 7-5, and Figure 7-6 show the analog signal chain performance of the cascaded LMH5401+LMH6401 path. Figure 7-7 shows the transformer coupling input performance with the ADC12DJ3200 ADC.

A. LMH5401 Gain = 12 dB

Figure 7-4 SNR versus FREQ (LMH6401 I/P Path)

A. LMH5401 Gain = 12 dB

Figure 7-5 SFDR versus FREQ (LMH6401 I/P Path)

A. LMH5401 Gain = 12 dB

Figure 7-6 THD versus FREQ (LMH6401 I/P Path) Figure 7-7 SNR, SFDR, THD versus FREQ (TRANSFORMER I/P)

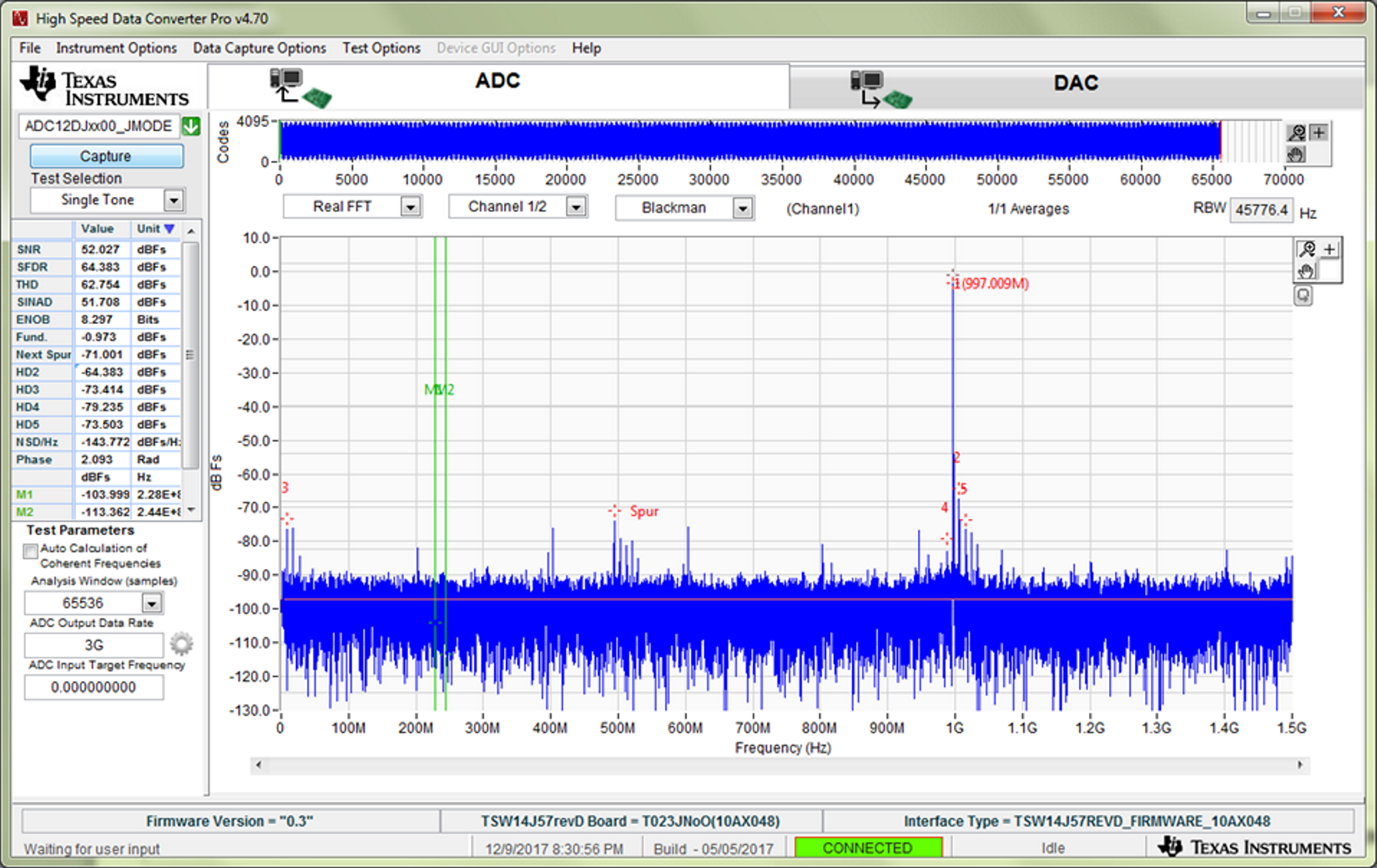

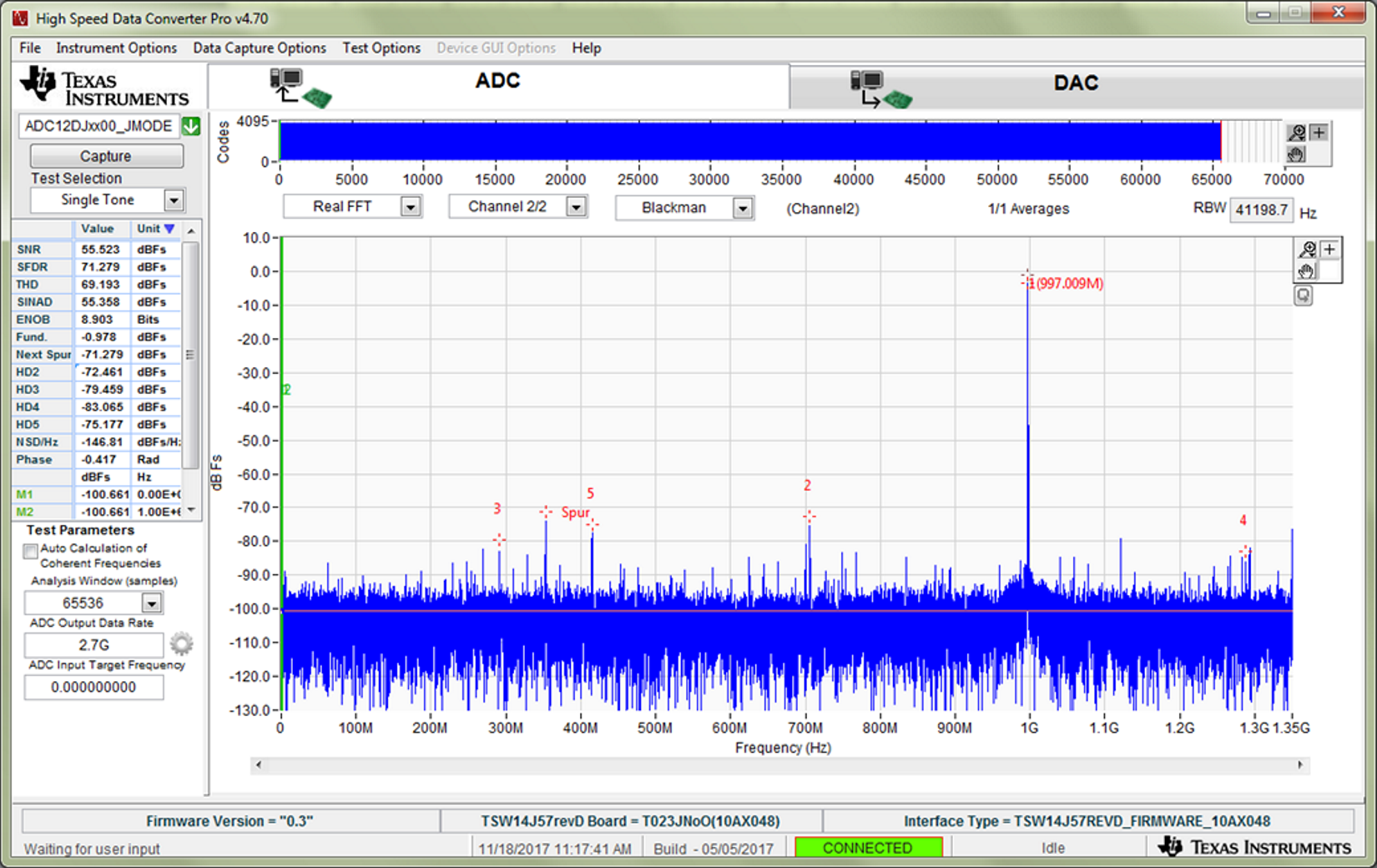

Figure 7-7 SNR, SFDR, THD versus FREQ (TRANSFORMER I/P)Figure 7-8 and Figure 7-9 show the measured spectrum of the TIDA-01022 design at a 997-MHz input signal for the LMH5401+LMH6401 combination and transformer coupling, respectively.

Figure 7-8 997-MHz Spectrum (LMH5401+LMH6401)

Figure 7-8 997-MHz Spectrum (LMH5401+LMH6401) Figure 7-9 997-MHz Spectrum (Transformer Coupling)

Figure 7-9 997-MHz Spectrum (Transformer Coupling)