SPRACS0A May 2020 – November 2022 TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28033 , TMS320F28033-Q1 , TMS320F28035 , TMS320F28035-EP , TMS320F28035-Q1 , TMS320F28053 , TMS320F28055 , TMS320F2806-Q1 , TMS320F28065 , TMS320F28069 , TMS320F28069-Q1 , TMS320F28069F , TMS320F28069F-Q1 , TMS320F28069M , TMS320F28069M-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.1 Handling Shared Resources Across C28x/CLA

CLA allows offloading of control tasks efficiently from C28x and enables concurrent control loop execution on C2000 devices with many other additional benefits as discussed in earlier sections. But it is important to note that the peripherals are still shared between them and concurrent read-modify-write to the shared registers can lead to data race conditions ultimately leading to data violation or incorrect functionality. Ideally it’s best to avoid any concurrent updates to the same peripheral by both CLA and C28x during run time but in case it is unavoidable, conflicts for shared resources must be handled carefully. The example “cla_ex7_shared_resource_handling” illustrates one such instance where both C28x and CLA do concurrent read-modify-write to same (AQCSFRC) register independently at different frequencies, which leads to a race condition between C28x and CLA and creates a possibility where updates due to one of them can get lost or overwritten. This is a standard critical section problem and can be handled using software handshaking mechanism like mutual exclusion but most of the real-time control applications are time-sensitive and cannot afford additional software cycles overhead. This example suggests an alternative hardware based technique to schedule the CLA and C28x tasks smartly in order to avoid overlapping access of shared resources. The hardware-based scheduling technique makes use of the programmable phase shifting mechanism of the EPWM modules.

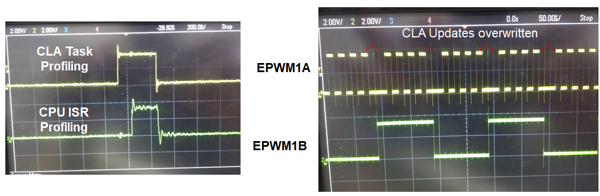

As depicted in Figure 5-6, C28x ISR and CLA task runs independently at 10 KHz and 100 KHz respectively. C28x ISR gets periodically triggered by EPWM4, and toggles the EPWM1B output via software by controlling CSFB bits of AQCSFRC. CLA task gets triggered by EPWM5 and toggles the EPWM1A output via software by controlling CSFA bits of AQCSFRC (refer to device TRM [1] for further details about this register). Thus in this process both C28x and CLA do overlapping read-modify-write to AQCSFRC register as can be observed form the profiling waveforms shown in Figure 5-7. As a result, the updates to the AQCSFRC due to CLA gets overwritten, which is very evident from the spikes observed in EPWM1A output waveform shown in Figure 5-7.

Figure 5-6 Concurrent R-M-W by C28x/CLA

Figure 5-6 Concurrent R-M-W by C28x/CLA Figure 5-7 Profiling and Output Waveforms With Phase-Shift Disabled

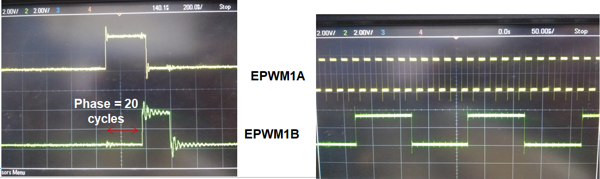

Figure 5-7 Profiling and Output Waveforms With Phase-Shift DisabledThe phase shifting mechanism of the EPWM modules, as shown in Figure 5-8, is utilized to schedule the CLA task and C28x ISR efficiently in order to resolve the above issue. EPWM4 generates a synchronous pulse every ZERO event and provides a phase shift of 20 cycles to EPWM5. This way both CLA task and C28x ISR runs at the original frequencies (100 KHz and 10 KHz), but CLA task leads with a phase offset of 20 cycles w.r.t C28x ISR as can be observed from the profiling waveform shown in Figure 5-9. Concurrent read-modify-writes to AQCSFRC never happens and the EPWM1A and EPWM1B outputs behave as desired without any distortion as shown in Figure 5-9. Thus the proposed hardware based scheduling technique helps to avoid data race conditions between C28x and CLA, and also helps to realize the true parallel execution of both processing engines by avoiding any simultaneous accesses and, hence maximizes the overall device performance.

Figure 5-8 EPWM-Based Phase-Shifting Technique

Figure 5-8 EPWM-Based Phase-Shifting Technique Figure 5-9 Profiling and Output Waveforms With Phase-Shift Enabled

Figure 5-9 Profiling and Output Waveforms With Phase-Shift Enabled