SPRACN0F October 2021 – March 2023 F29H850TU , F29H859TU-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- The Essential Guide for Developing With C2000™ Real-Time Microcontrollers

- Trademarks

- 1C2000 and Real-Time Control

-

2Sensing Key Technologies

- 2.1 Accurate Digital Domain Representation of Analog Signals

- 2.2 Optimizing Acquisition Time vs Circuit Complexity for Analog Inputs

- 2.3 Hardware Based Monitoring of Dual-Thresholds Using a Single Pin Reference

- 2.4 Resolving Tolerance and Aging Effects During ADC Sampling

- 2.5 Realizing Rotary Sensing Solutions Using C2000 Configurable Logic Block

- 2.6 Smart Sensing Across An Isolation Boundary

- 2.7 Enabling Intra-Period Updates in High Bandwidth Control Topologies

- 2.8 Accurate Monitoring of Real-Time Control System Events Without the Need for Signal Conditioning

-

3Processing Key Technologies

- 3.1 Accelerated Trigonometric Math Functions

- 3.2 Fast Onboard Integer Division

- 3.3 Hardware Support for Double-Precision Floating-Point Operations

- 3.4 Increasing Control Loop Bandwidth With An Independent Processing Unit

- 3.5 Flexible System Interconnect: C2000 X-Bar

- 3.6 Improving Control Performance With Nonlinear PID Control

- 3.7 Understanding Flash Memory Performance In Real-Time Control Applications

- 3.8 Deterministic Program Execution With the C28x DSP Core

- 3.9 Efficient Live Firmware Updates (LFU) and Firmware Over-The-Air (FOTA) updates

-

4Control Key Technologies

- 4.1 Reducing Limit Cycling in Control Systems With C2000 HRPWMs

- 4.2 Shoot Through Prevention for Current Control Topologies With Configurable Deadband

- 4.3 On-Chip Hardware Customization Using the C2000 Configurable Logic Block

- 4.4 Fast Detection of Over and Under Currents and Voltages

- 4.5 Improving System Power Density With High Resolution Phase Control

- 4.6 Safe and Optimized PWM Updates in High-Frequency, Multi-Phase and Variable Frequency Topologies

- 4.7 Solving Event Synchronization Across Multiple Controllers in Decentralized Control Systems

- 5Interface Key Technologies

- 6Safety Key Technologies

- 7References

- 8Revision History

4.4.2 In Depth

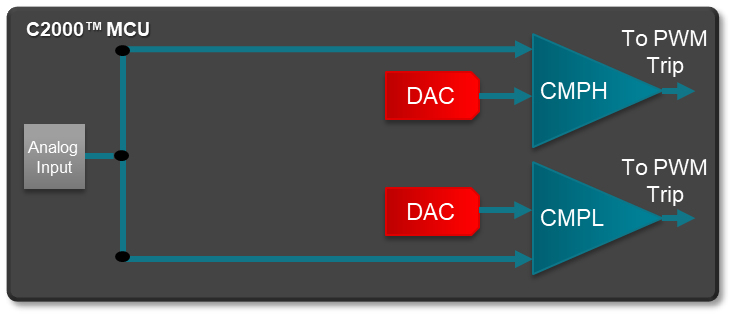

Fault detection and reaction is important in most systems, not only for avoiding an undefined output, but for preventing damage to components both on and off the main Printed Circuit Board (PCB). The speed at which the fault detection takes place, as well as the final FET output state change, is critical to the system. A dedicated subsystem that ties together the analog and digital domains has been implemented on the C2000 MCU for handling this requirement: the Comparator Subsystem or CMPSS (#T5843526-91).

Figure 4-6 CMPSS Visualization

Figure 4-6 CMPSS VisualizationThere are up to eight CMPSS modules on each C2000 MCU, with internal DACs that give the inverting/comparison detection level for the line that is being monitored. As shown in #T5843526-91, each CMPSS module has two comparators for simultaneous high and low detection. Using the CMPSS has several advantages over using the ADC for fault detection:

- System Overhead: Using the CMPSS to monitor a pin is an essentially zero overhead operation after the initial setup. The pin is always monitored against the comparison value until disabled. Other techniques would require periodic ADC conversions and threshold checking.

- Latency: While the ADC sampling rate can be simply factored into the period of the control loop, there is not a deterministic constant to a fault condition. As such there will be an inherent delay to detect the fail, both from a point of sample to the conversion time of the ADC itself. The comparator has no such trigger requirement or sample time, it is continuously monitoring the analog signal.

- Dedicated PWM Trip Zone input: The output of every CMPSS module can be tied directly into the Trip Zone of any PWM, and the action when the signal is received is configurable in software. This means there is no software overhead as there would be in processing an ADC ISR to then create the action to the PWM in software.

- No clock dependence: Since by definition a comparator is a

purely analog domain circuit there are not clock dependencies to the changing

state of its output based on the input. The C2000 MCU has carried this forward

to give a asynchronous path from the comparator to the PWM. This allows for the

fastest possible time from fault detection to pin state change, in addition to

removing any clock dependence (Table 4-2). Table 4-2 Comparison of Fault Detection and Trip Methods

Sampling Method Sample Time (min) Result Ready (min) Latch and Change PWM Pin (@200 MHz SysClk) Total Time From Fault To Trip 12-bit ADC 75 ns 260 ns approximately 100 ns(inc ISR) 435 ns 12-bit ADC w/PPB 75 ns 260 ns 10 ns 355 ns CMPSS NA NA NA 60 ns - Simultaneous high and low detection: Each input to a CMPSS module routes the signal to two physically independent comparators that give the ability to detect both overshoot and undershoot at the same time.