SPRACW5A April 2021 – December 2021 F29H850TU , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Trademarks

- 1Introduction

- 2ACI Motor Control Benchmark Application

- 3Real-time Benchmark Data Analysis

-

4C2000 Value Proposition

- 4.1 Efficient Signal Chain Execution With Better Real-Time Response Than Higher Computational MIPS Devices

- 4.2 Excellent Real-Time Interrupt Response With Low Latency

- 4.3 Tight Peripheral Integration That Scales Applications With Large Number of Peripheral Accesses

- 4.4 Best in Class Trigonometric Math Engine

- 4.5 Versatile Performance Boosting Compute Engine (CLA)

- 4.6 Deterministic Execution due to Low Execution Variance

- 5Summary

- 6References

- 7Revision History

3.3 TMU (math enhancement) Impact

Many C2000 targets have a math extension called Trigonometric Math Unit (TMU) ,which is an extension of the Floating-Point Unit (FPU) and enhances the instruction set of the C28x+FPU by efficiently executing trigonometric and arithmetic operations that are commonly used in control system applications.

The ACI motor control application has control algorithms: Park, Inverse Park and Flux estimator that involve trigonometric math. To demonstrate the impact that the TMU can make, the F28004x has two build configurations SignalChain_RAM_TMU and SignalChain_RAM_FastRTS.

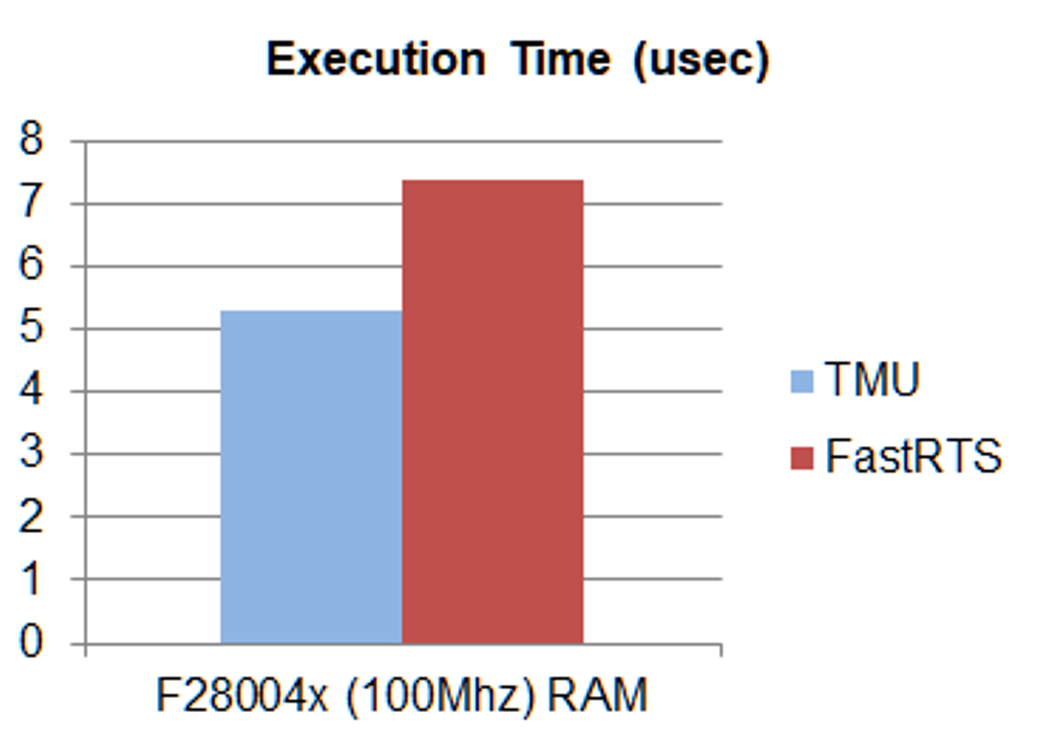

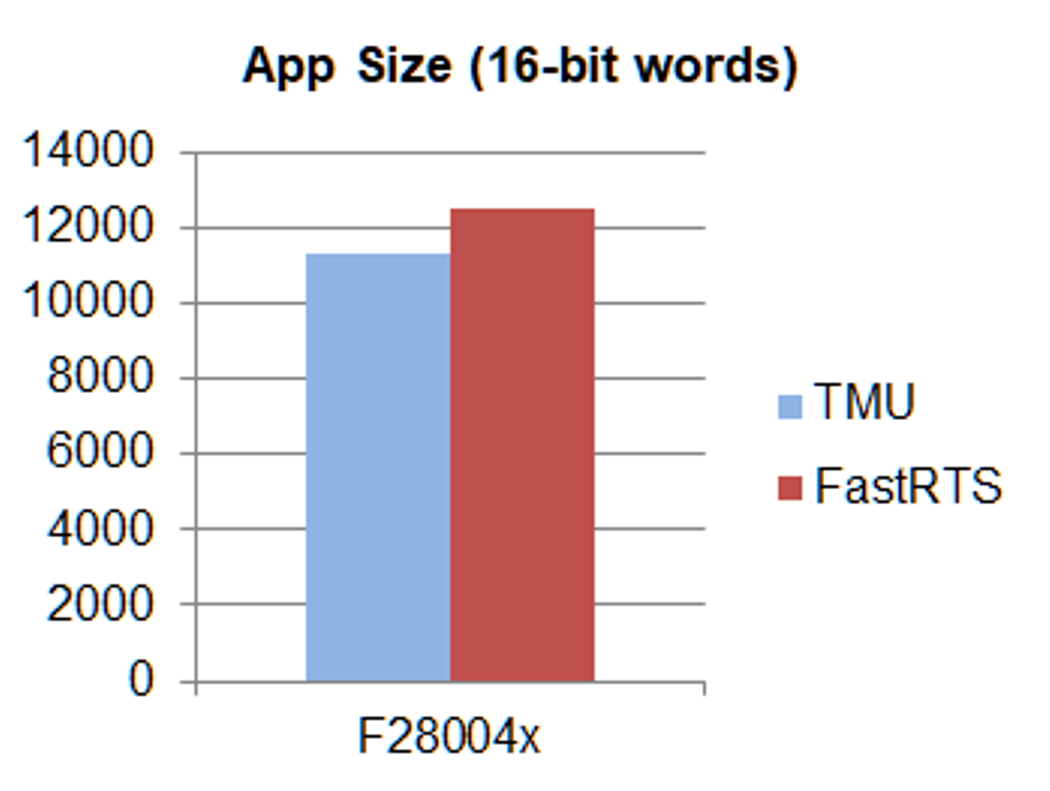

In the following figures, Figure 3-4 shows the execution time derived from the benchmark cycles data and Figure 3-5 shows application size (code and data) for the control code (driver libraries and runtime are excluded) as indicated in the compiler tools generated linker map file, for each of the two configurations.

Figure 3-4 Control Loop Execution

Time Out of RAM With TMU and FastRTS

Figure 3-4 Control Loop Execution

Time Out of RAM With TMU and FastRTS Figure 3-5 Application Size Compiled

for TMU and FastRTS

Figure 3-5 Application Size Compiled

for TMU and FastRTSThe data in the graphs show that the TMU has a two-fold impact:

- Faster Execution Time: The execution of the application becomes faster by 28%.

- Smaller Application Size: A typical trigonometric implementation involves lookup tables and floating-point computations to calculate common trigonometric operations. The TMU provides instructions for these trigonometric operations and eliminates both the lookup tables and complex floating point code. This translates into smaller application size allowing smaller memory devices with TMU to be able to support the application. In this particular example the application size reduces by 14%.