Packaging information

| Package | Pins CFP (HSL) (HBE) | 64 |

| Operating temperature range (°C) 25 to 25 |

| Package qty | Carrier 24 | TUBE |

Features for the DP83561-SP

- QML Class V (QMLV), RHA, SMD 5962-20216

- Military temperature range: –55°C to 125°C

- Radiation performance

- RHA up to TID = 300 krad (Si)

- SEL immune to LET = 121 MeV·cm2/mg

- Single Event Functional Interrupt (SEFI) monitor

suite

- Monitor

- IEEE PCS state machine monitors

- ECC configuration register monitor

- PLL lock monitor

- On-chip temperature monitor

- Action

- Interrupt pins to monitor events

- Correction

- ECC-protected configuration registers

- Pin-configurable automatic SEFI recovery

- Serial Management Interface (SMI) disable

- Monitor

- Fully compatible to IEEE802.3 1000BASE-T, 100BASE-TX and 10BASE-Te specifications

- Low RGMII latency (Tx < 90 ns, Rx < 290 ns)

- Time sensitive network compliant

- MAC interface: RGMII, MII

- Integrated MDI termination resistors

- Programmable RGMII termination impedance

- Power supply: 2.5 V, 1.8 V, 1.1 V

- I/O voltages: 1.8 V, 2.5 V, and 3.3 V

- 25-MHz or 125-MHz synchronized clock output

- Cable diagnostics: open, short using TDR

- JTAG support

Description for the DP83561-SP

The DP83561-SP is a high reliability gigabit ethernet PHY designed for the high-radiation environment of space. The DP83561-SP is a low power, fully featured physical layer transceiver with integrated PMD sub-layers to support 10BASE-Te, 100BASE-TX and 1000BASE-T Ethernet protocols.

The DP83561-SP is designed for easy implementation of 10/100/1000 Mbps Ethernet LANs in extremely hostile environments. It interfaces directly to twisted pair media through an external transformer. This device interfaces directly to the MAC layer through Reduced GMII (RGMII) and MII.

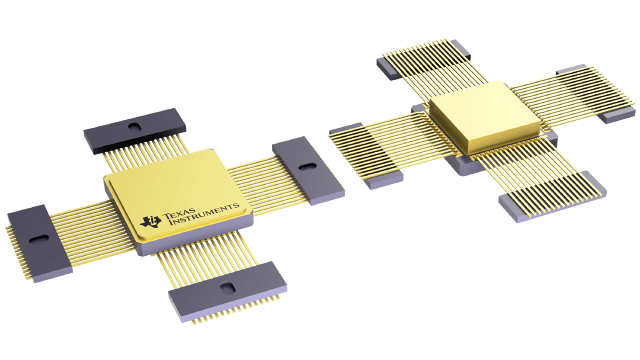

The device is Radiation Hardened by Design (RHBD), fabricated by Texas Instruments using a CMOS process, and is available in 64-pin Ceramic Quad Flat Pack (CQFP) package, with a 11-mm × 11-mm body size (nominal).