SLUA963B June 2020 – October 2022 UCC21710-Q1 , UCC21732-Q1 , UCC5870-Q1

- HEV/EV Traction Inverter Design Guide Using Isolated IGBT and SiC Gate Drivers

- 1Introduction

- 2HEV/EV Overview

-

3Design of HEV/EV Traction Inverter Drive Stage

- 3.1 Introduction to UCC217xx-Q1

- 3.2 Designing a Traction Inverter Drive System Using UCC217xx-Q1

- 3.3 Description of Protection Features

- 3.4 Protection Features of UCC217xx-Q1

- 3.5

UCC217xx-Q1 Protection and Monitoring Features Descriptions

- 3.5.1 Primary and Secondary Side UVLO and OVLO

- 3.5.2 Over-Current (OC) and Desaturation (DESAT) Detection

- 3.5.3 2-Level and Soft Turn-Off

- 3.5.4 Power Switch Gate Voltage (VGE/VGS) Monitoring

- 3.5.5 Power Switch Anti-Shoot-Through

- 3.5.6 Integrated Internal or External Miller Clamp

- 3.5.7 Isolated Analog-to-PWM Channel

- 3.5.8 Short-Circuit Clamping

- 3.5.9 Active Pulldown

- 3.6 Introduction to UCC5870-Q1

- 3.7 Designing a Traction Inverter Drive System Using UCC5870-Q1

- 3.8 Description of Protection Features

- 3.9 Protection Features of UCC5870-Q1

- 3.10

UCC5870-Q1 Protection and Monitoring Features Descriptions

- 3.10.1 Primary and Secondary Side UVLO and OVLO

- 3.10.2 Programmable Desaturation (DESAT) Detection and Over-Current (OC)

- 3.10.3 Adjustable 2-Level or Soft Turn-Off

- 3.10.4 Active High-Voltage Clamp

- 3.10.5 Power Switch Gate Voltage (VGE/VGS) Monitoring

- 3.10.6 Gate Threshold Voltage Monitor

- 3.10.7 Power Switch Anti-Shoot-Through

- 3.10.8 Active Short Circuit (ASC)

- 3.10.9 Integrated Internal or External Miller Clamp

- 3.10.10 Isolated Analog-to-Digital Converter

- 3.10.11 Short-Circuit Clamping

- 3.10.12 Active and Passive Pulldown

- 3.10.13 Thermal Shutdown and Temperature Warning of Driver IC

- 3.10.14 Clock Monitor and CRC

- 3.10.15 SPI and Register Data Protection

- 4Isolated Bias Supply Architecture

- 5Summary

- 6References

- 7Revision History

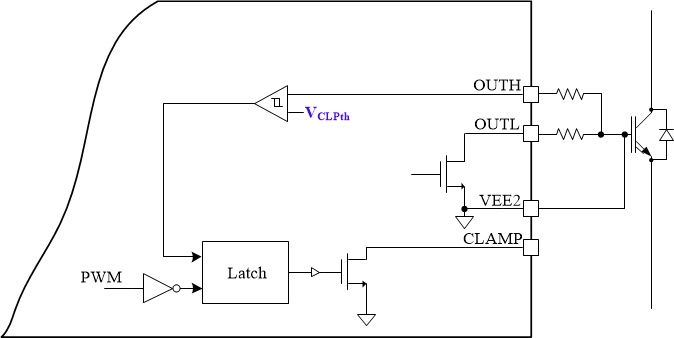

3.10.9 Integrated Internal or External Miller Clamp

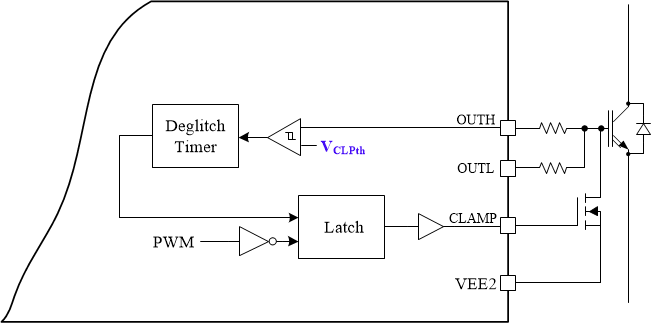

The Active Miller clamp (CLAMP) is used to prevent the power transistor from false turn-on due to Miller capacitance-induced current. The active Miller clamp adds a low impedance path between power transistor gate terminal and VEE2 to pull the gate of the external FET hard to VEE2, bypassing any external gate resistors. The Miller clamp engages when the OUTH pin falls below VCLPTH, which is the threshold voltage that can be selected using SPI programming. The integrated internal Miller Clamp is shown in Figure 3-25. The CLAMP pin can also be configured to drive an external Miller Clamp FET if more pull-down strength is required, as shown in Figure 3-26. The external Miller Clamp FET also provides the ability to optimize placement of the clamp such that it is very close to the gate of the power transistor. Both options can be easily tested by configuring the output using SPI and making minor changes to the layout.

Figure 3-25 Integrated Internal Miller Clamp

Figure 3-25 Integrated Internal Miller Clamp Figure 3-26 Integrated Driver for External Miller Clamp

Figure 3-26 Integrated Driver for External Miller Clamp