SPRACZ0A August 2021 – March 2023 F29H850TU , F29H850TU , F29H859TU-Q1 , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800132 , TMS320F2800133 , TMS320F2800133 , TMS320F2800135 , TMS320F2800135 , TMS320F2800137 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280023C , TMS320F280025 , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280033 , TMS320F280034 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C , TMS320F280049C-Q1 , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28076 , TMS320F28374D , TMS320F28374D , TMS320F28374S , TMS320F28374S , TMS320F28375D , TMS320F28375D , TMS320F28375S , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376D , TMS320F28376S , TMS320F28376S , TMS320F28377D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378D , TMS320F28378S , TMS320F28378S , TMS320F28379D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28379S , TMS320F28384D , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388D , TMS320F28388S , TMS320F28388S , TMS320F28P550SG , TMS320F28P550SG , TMS320F28P550SJ , TMS320F28P550SJ , TMS320F28P559SG-Q1 , TMS320F28P559SG-Q1 , TMS320F28P559SJ-Q1 , TMS320F28P559SJ-Q1 , TMS320F28P650DH , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

-

1Introduction

- 1.1

Resources

- 1.1.1 TINA-TI SPICE-Based Analog Simulation Program

- 1.1.2 PSPICE for TI Design and Simulation Tool

- 1.1.3 Application Report: ADC Input Circuit Evaluation for C2000 MCUs

- 1.1.4 TI Precision Labs - SAR ADC Input Driver Design Series

- 1.1.5 Analog Engineer's Calculator

- 1.1.6 TI Precision Labs - Op Amps: Stability Series

- 1.1.7 Related Application Reports

- 1.1.8 Comparison of Schematic Capture and Simulation Tools

- 1.1.9 PSpice for TI ADC Input Models

- 1.1

Resources

-

2Charge-Sharing Concept

- 2.1 Traditional High-Speed ADC Driving Circuits

- 2.2 Increased Cs in High-Speed ADC Driving Circuits

- 2.3 Very Large Cs in ADC Driving Circuits

- 2.4 Charge-Sharing Operation

- 2.5 Sample Rate and Source Impedance vs. Tracking Error

- 2.6 Analytical Solution to Tracking Error

- 2.7 Charge-Sharing in Multiplexed ADCs

- 2.8 Charge-Sharing Circuit Advantages

- 2.9 Charge-Sharing Circuit Disadvantages

- 3Charge Sharing Design Flow

- 4Charge-Sharing Circuit Simulation Methods

- 5Example Circuit Designs

- 6Summary

- A Appendix: ADC Input Settling Motivation

- References

- Revision History

4.3 Bias Point Analysis to Determine Voa_ss

Charge-sharing settling input designs do not always include an op-amp, but when the signal chain of interest does, steps must be taken to account for the DC voltage errors modeled in the PSpice for TI models. This ensures that the simulation only measures settling performance. To accomplish this, it is necessary to determine the steady-state output value for Voa given the specific op-amp being included. This value must then be copied to the Voa_ss voltage source.

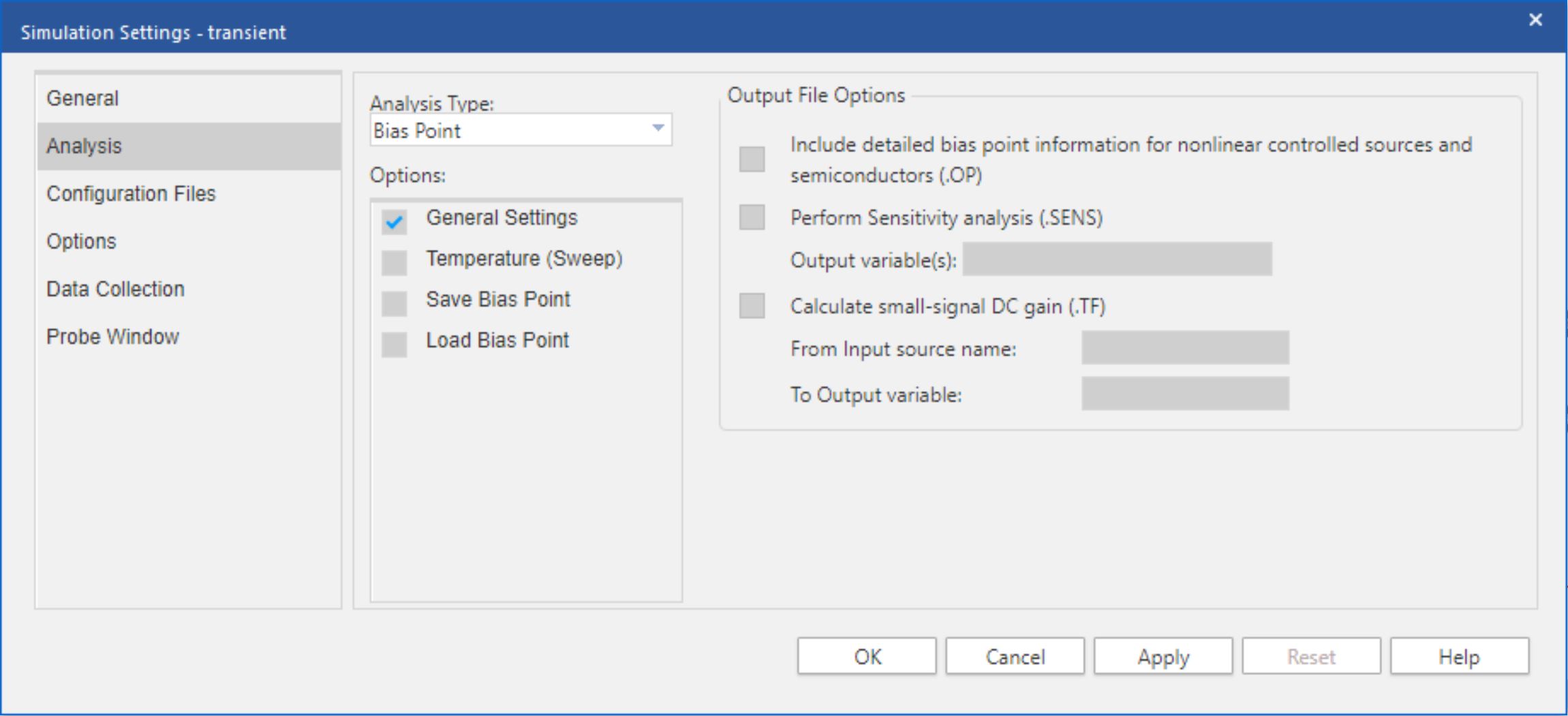

Perform a bias point analysis to determine the steady-state output value for Voa given the specific op-amp being included. Performing a bias point analysis in PSpice for TI requires the creation of a Bias Point simulation profile. Once the simulation profile is created, go to PSpice ➔ Run to perform the analysis. Perform a bias point analysis using the simulation profile shown in Figure 4-5.

Figure 4-5 Bias Point Analysis Simulation

Profile

Figure 4-5 Bias Point Analysis Simulation

ProfileIf the bias point analysis does not converge, then a transient analysis must be performed instead to determine the steady-state output value for Voa given the specific op-amp being included. Close the PSpice for TI simulation window and refer to the next section, Section 4.4, for instructions on how to proceed. If the bias point analysis converges, close the PSpice for TI simulation window. Using the menu in the upper left of the PSpice for TI schematic capture window, go to PSpice ➔ Bias Points and enable bias voltage display. The bias voltages should appear as shown in Figure 4-6.

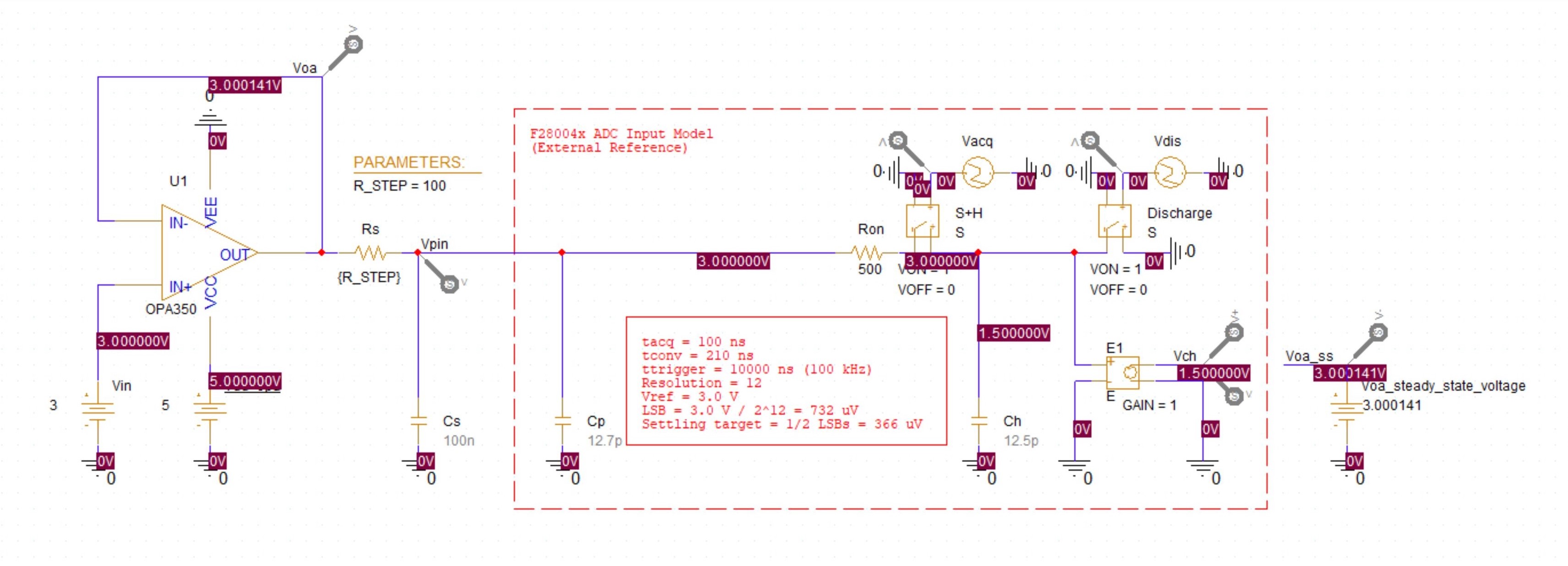

Figure 4-6 Bias Point Analysis

Results

Figure 4-6 Bias Point Analysis

ResultsThe bias voltage of the node at the output of the specific op-amp being included is the steady-state output value for Voa. For OPA350 in this circuit, this procedure gives:

- Voa = 3.000141 V

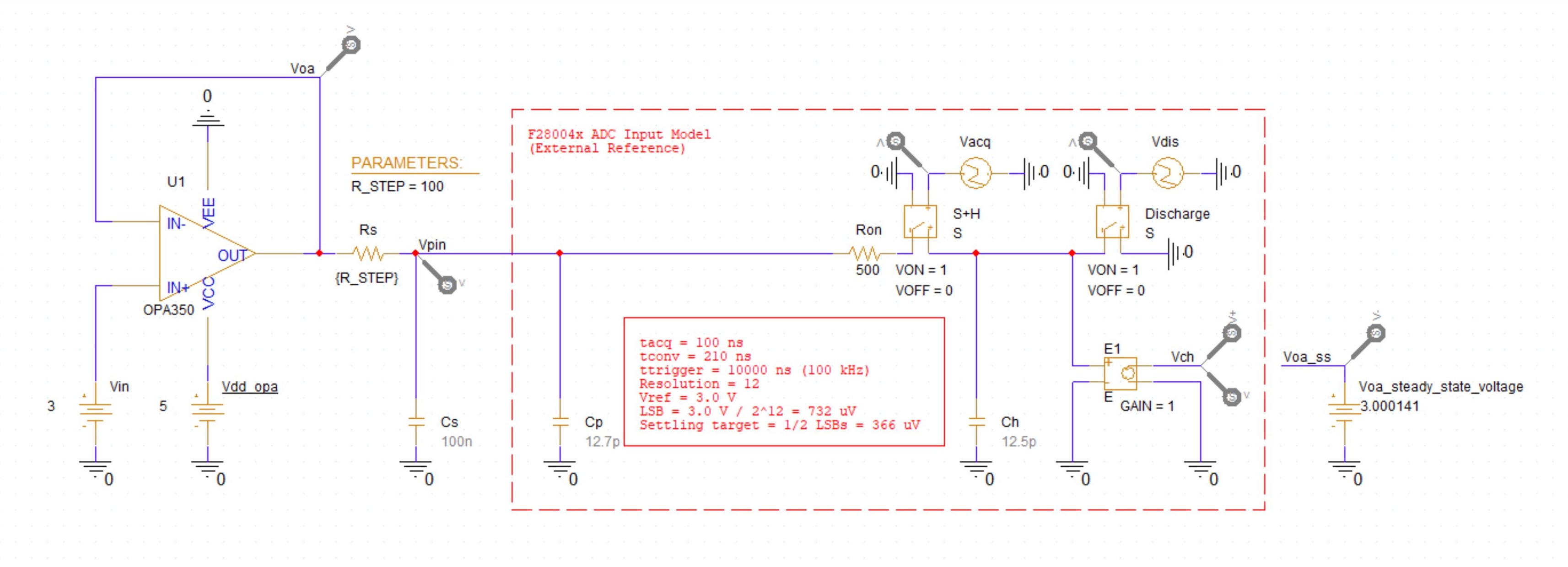

Copy this value to the Voa_ss voltage source as shown in Figure 4-7.

Because the steady-state output value for Voa given the specific op-amp being included is known, skip the next section, Section 4.4, and refer to Section 4.5 for instructions on how to proceed.

Figure 4-7 Nodal Analysis Example

Figure 4-7 Nodal Analysis Example