SLVAE87B December 2020 – June 2025 BQ79600-Q1 , BQ79612-Q1 , BQ79614-Q1 , BQ79616-Q1 , BQ79652-Q1 , BQ79654-Q1 , BQ79656-Q1

- 1

- Abstract

- Trademarks

- 1 NPN LDO Supply

- 2 AVDD, CVDD Outputs and DVDD, NEG5, REFHP and REFHM

- 3 OTP Programming

- 4 Cell Voltage Sense (VCn) and Cell Balancing (CBn)

- 5 Bus Bar Support

- 6 TSREF

- 7 General Purpose Input-Output (GPIO) Configurations

- 8 Base and Bridge Device Configuration

- 9 Daisy-Chain Stack Configuration

- 10Multidrop Configuration

- 11Main ADC Digital LPF

- 12AUX Anti Aliasing Filter (AAF)

- 13Layout Guidelines

- 14BCI Performance

- 15Common and Differential Mode Noise

- 16Summary

- 17References

- 18Revision History

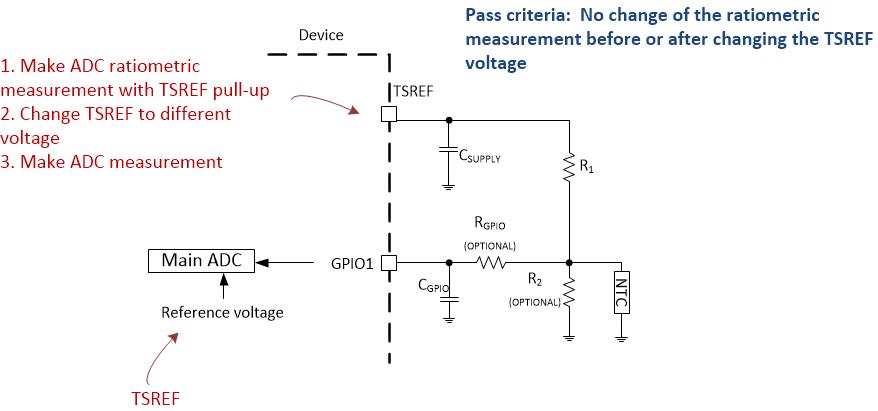

7.1 Ratiometric Temperature Measurement

Ratiometric voltage measurement is most commonly used for external temperature sensing. To measure an external temperature sensor, the GPIO connections must have a resistor divider from TSREF to AVSS with the GPIO connected to the center tap. The NTC can then be connected from TSREF to GPIO or from GPIO to AVSS. Optionally, the GPIO input can be filtered using a low-pass filter (CGPIO and RGPIO) to reduce high-frequency noise as shown Figure 7-1.

Figure 7-1 GPIO Ratiometric Measurement

Figure 7-1 GPIO Ratiometric MeasurementThe main ADC measures TSREF and GPIO voltages in the round robin. A microcontroller calculates the ratiometric voltage by Equation 6.

Temperature accuracy is affected by ADC measurement error and external component error. Using ratiometric measurement greatly reduces the ADC measurement error. Furthermore, the better the tolerance of the external circuit, the more accurate temperature sensing.