JAJSQN0 june 2023 CDCE6214Q1TM

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要 (続き)

- 6 デバイスの比較

- 7 ピン構成および機能

-

8 仕様

- 8.1 絶対最大定格

- 8.2 ESD 定格

- 8.3 推奨動作条件

- 8.4 熱に関する情報

- 8.5 EEPROM の特性

- 8.6 リファレンス入力、シングルエンド特性

- 8.7 リファレンス入力、差動特性

- 8.8 リファレンス入力、水晶振動子モードの特性

- 8.9 汎用入力特性

- 8.10 トリプル・レベル入力特性

- 8.11 ロジック出力特性

- 8.12 フェーズ・ロック・ループ特性

- 8.13 閉ループ出力ジッタの特性

- 8.14 入力および出力絶縁

- 8.15 バッファ・モードの特性

- 8.16 PCIe スペクトラム拡散ジェネレータ

- 8.17 LVCMOS 出力特性

- 8.18 LP-HCSL 出力特性

- 8.19 LVDS 出力特性

- 8.20 出力同期特性

- 8.21 パワーオン・リセット特性

- 8.22 I2C 互換シリアル・インターフェイスの特性

- 8.23 タイミング要件、I2C 互換シリアル・インターフェイス

- 8.24 電源特性

- 8.25 代表的特性

- 9 パラメータ測定情報

- 10詳細説明

- 11アプリケーションと実装

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGE|24

サーマルパッド・メカニカル・データ

- RGE|24

発注情報

10.3.1.1 ゼロ遅延モード、内部パスおよび外部パス

CDCE6214Q1TM は、内部および外部フィードバックにより、ゼロ遅延モードで動作できます。ゼロ遅延モードでは、PRIREF クロックが PFD への基準クロックとして使用されます。SECREF 入力クロックを使用して、外部ソースを PFD へのフィードバック・クロックとして供給できます。ゼロ遅延動作には、外部フィードバック・パスを推奨します。さらに、出力チャネル 2 から供給される追加の内部フィードバック・パスもあります。内部ゼロ遅延モードでは、外部ゼロ遅延モードよりも入力出力伝搬遅延が長くなることが予想されます。

表 10-2 ゼロ遅延動作

| 動作(1)(2) | REFSEL | R2[1:0] - REFSEL_SW | R24[1:0] - IP_SECREF_BUF_SEL(3) | R24[15] - IP_PRIREF_BUF_SEL(3) | R0[8] - ZDM_EN | R0[10] - ZDM_CLOCKSEL | 説明 |

|---|---|---|---|---|---|---|---|

| 通常動作、XTAL 入力 | L | 0h、1h、または 2h | 0h | X | 0h | 0h | 通常動作、XTAL 入力 |

| 通常動作、差動入力 | L | 0h、1h、または 2h | 2h または 3h | X | 0h | 0h | SECREF / 差動入力 |

| 通常動作、差動入力 | H | 0h、1h、または 3h | X | 1h | 0h | 0h | PRIREF / 差動入力 |

| 通常動作、LVCMOS 入力 | L | 0h、1h、または 2h | 1h | X | 0h | 0h | SECREF/LVCMOS 入力 |

| 通常動作、LVCMOS 入力 | H | 0h、1h、または 3h | X | 0h | 0h | 0h | PRIREF/LVCMOS 入力 |

| 外部ゼロ遅延モード、差動入力 | H | 0h、1h、または 3h | 2h または 3h | 1h | 1h | 1h | PRIREF の入力クロック、SECREF のフィードバック・クロック |

| 外部ゼロ遅延モード、LVCMOS 入力 | H | 0h、1h、または 3h | 1h | 0h | 1h | 1h | PRIREF の入力クロック、SECREF のフィードバック・クロック |

| 内部ゼロ遅延モード、差動入力 | H | 0h、1h、または 3h | X | 1h | 1h | 0h | PRIREF の入力クロック |

| 内部ゼロ遅延モード、差動入力 | H | 0h、1h、または 3h | X | 0h | 1h | 0h | PRIREF の入力クロック |

(1) ゼロ遅延モードでは、PLL がロックできるようにすべての分周器をプログラムする必要があります。ゼロ遅延モードでのパワーアップ時に、PLL は自動的にロックされます

(2) 内部ゼロ遅延モードでは、チャネル 2 が必要です。チャネル 2 はパワーダウンしないでください

(3) 「X」は、設定可能な任意のビット・フィールド値を取ります。機能に影響はありません

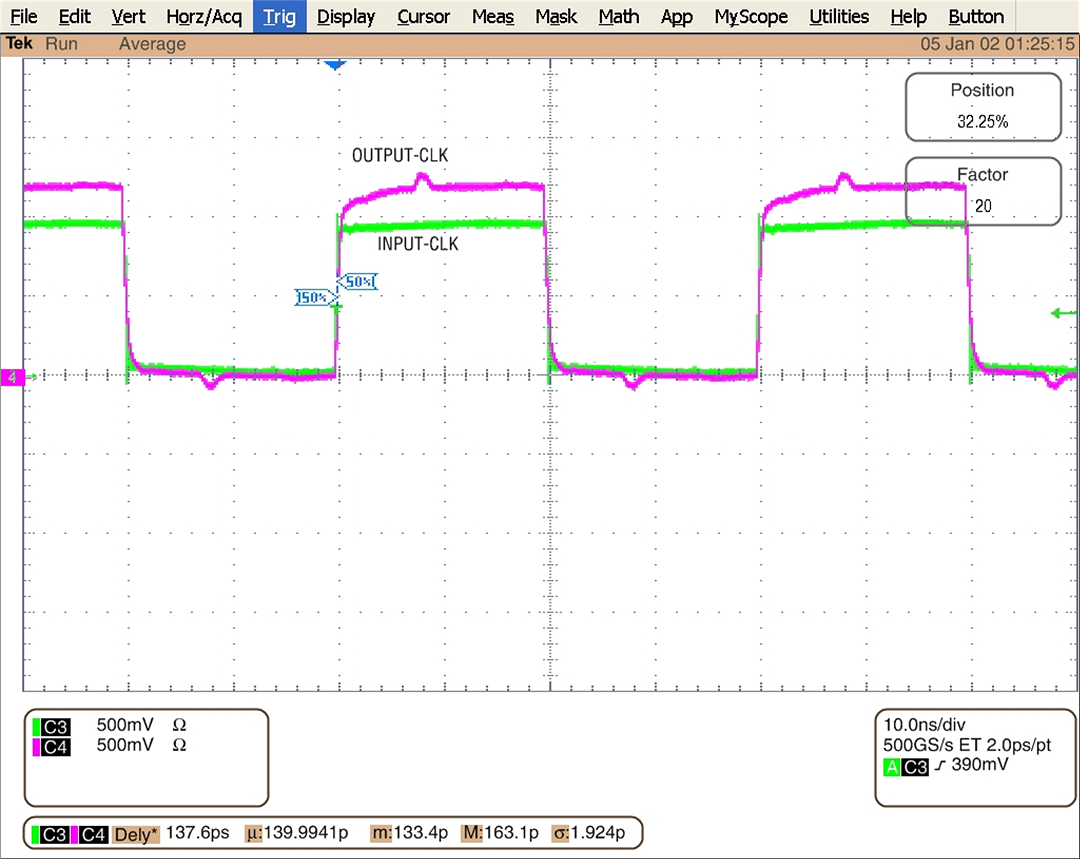

図 10-2 LVCMOS 出力の外部ゼロ遅延モードでの入力 / 出力アライメント

図 10-2 LVCMOS 出力の外部ゼロ遅延モードでの入力 / 出力アライメント